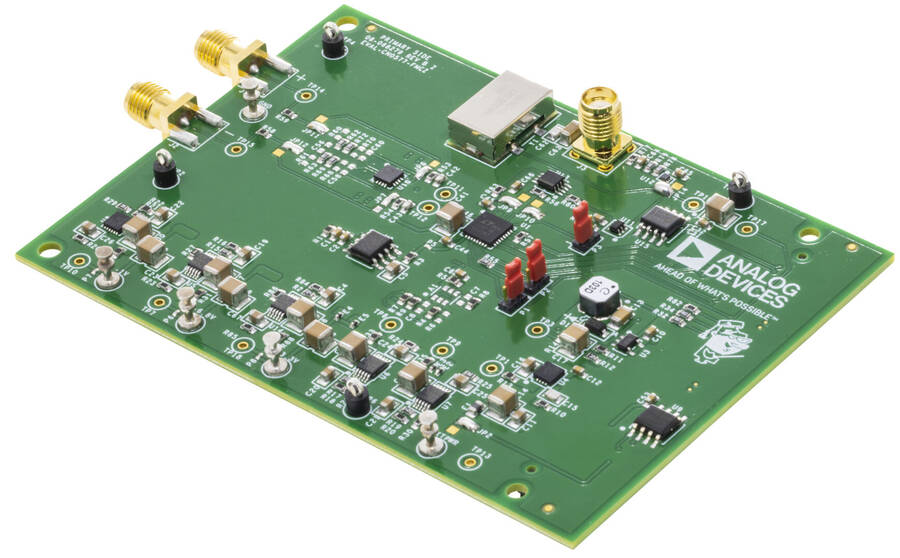

EVAL-CN0577-FMCZ

Analog Front End and Digital Interface for Serial LVDS SAR ADCs.

Overview

Instrumentation applications such as flow cytometry, optical pulse measurement, fast control loops, fast digital distortion correction, and image sensor digitization present unique data acquisition challenges. These applications often require a combination of high sample rate, high linearity, low drift, low noise, and low latency.

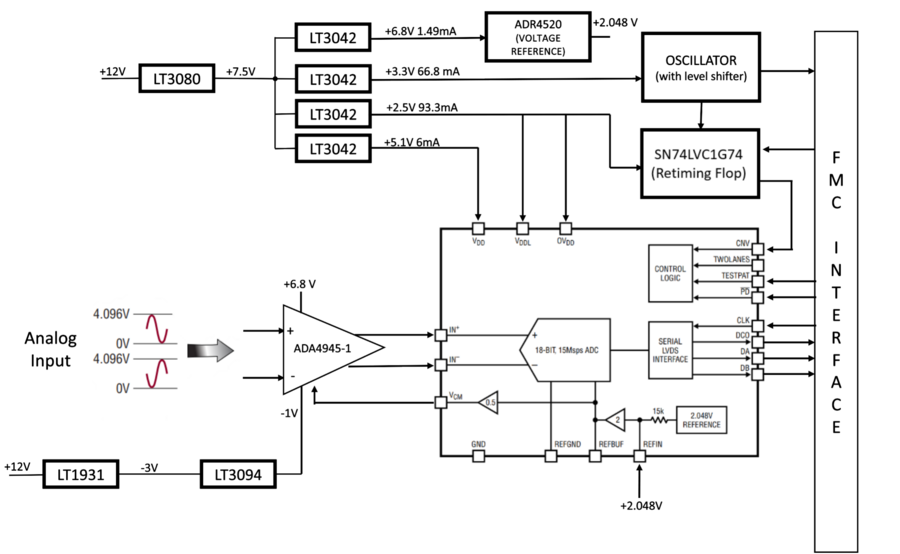

The EVAL-CN0577-FMCZ is an 18-bit, 15 MSPS, 2 ppm linear data acquisition system with an easy to drive input impedance of 1.1 kΩ. The analog input range is 8.096 V peak-to-peak and can be driven in either single-ended or differential mode, providing flexibility for many different applications.

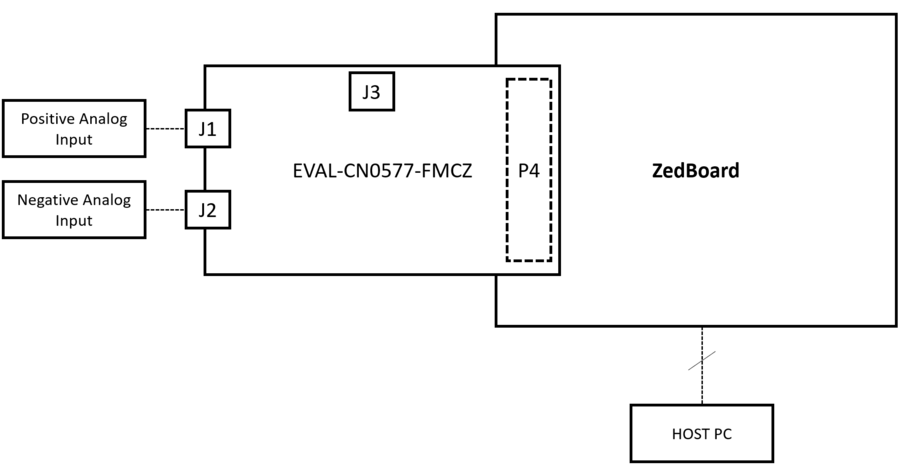

The circuit is in field programmable gate array (FPGA) mezzanine card (FMC) form factor, powered with 12 V either from the FMC connector or an external supply. The digital interface uses serial low voltage differential signaling (LVDS), minimizing the input/output requirements and enabling easy integration with other FPGA designs.

A separate data clock eases the timing requirements of the host FPGA. An on-board 120 MHz clock is forwarded to the FPGA and a CONVERT retiming flip-flop reduces jitter from the convert signal of the FPGA.

Features:

15 MSPS Throughput Rate

Guaranteed 18-Bit, No Missing Codes

No Pipeline Delay, No Cycle Latency

96 dB SNR (Typical)

164.5 dB dynamic range

2 ppm INL (Typical)

Serial LVDS Digital Interface

Flexible analog input drive (single-ended or differential mode)

On-board 120 MHz precision voltage-controlled crystal oscillator (VCXO)

Applications:

Flow cytometry

Optical pulse measurement

Fast control loops

Fast digital distortion correction

Image sensor digitization

Recommendations

People who follow the flow that is outlined have a much better experience with things. However, like many things, documentation is never as complete as it should be. If you have any questions, feel free to ask on our EngineerZone, but before that, please make sure you read our documentation thoroughly.

Table of contents

Block diagram

Reference Demos & Software

More Information and Useful Links

Registration

Receive software update notifications, documentation updates, view the latest videos, and more when you register your hardware. Register to receive all these great benefits and more!

HDL Reference design

The HDL Reference Design is documented at CN0577 HDL project.

Warning

All the products described on this page include ESD (electrostatic discharge) sensitive devices. Electrostatic charges as high as 4000V readily accumulate on the human body or test equipment and can discharge without detection. Although the boards feature ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality. This includes removing static charge on external equipment, cables, or antennas before connecting to the device.

Help and support

For questions and more information, please visit the EngineerZone technical support community.