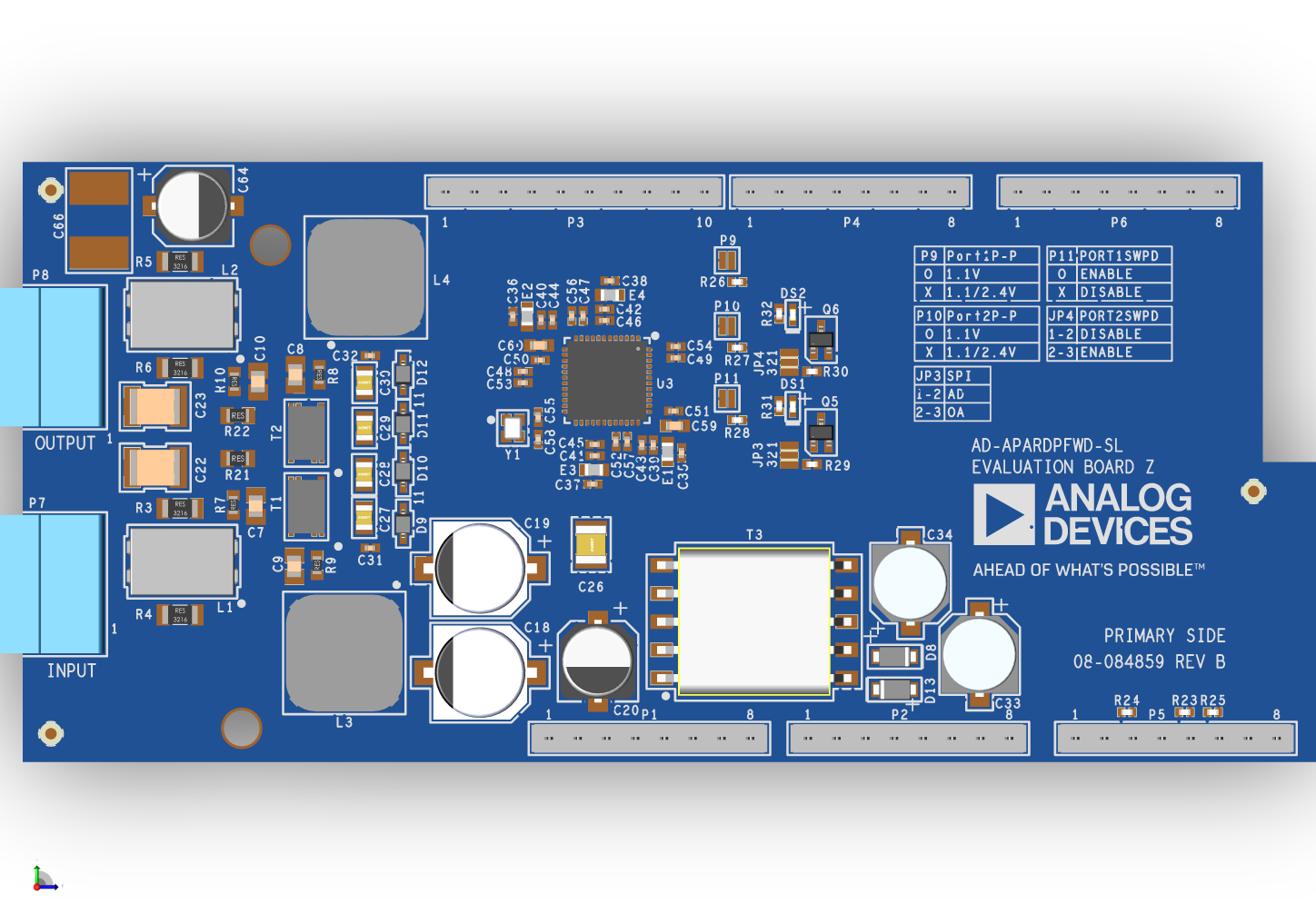

Primary Side

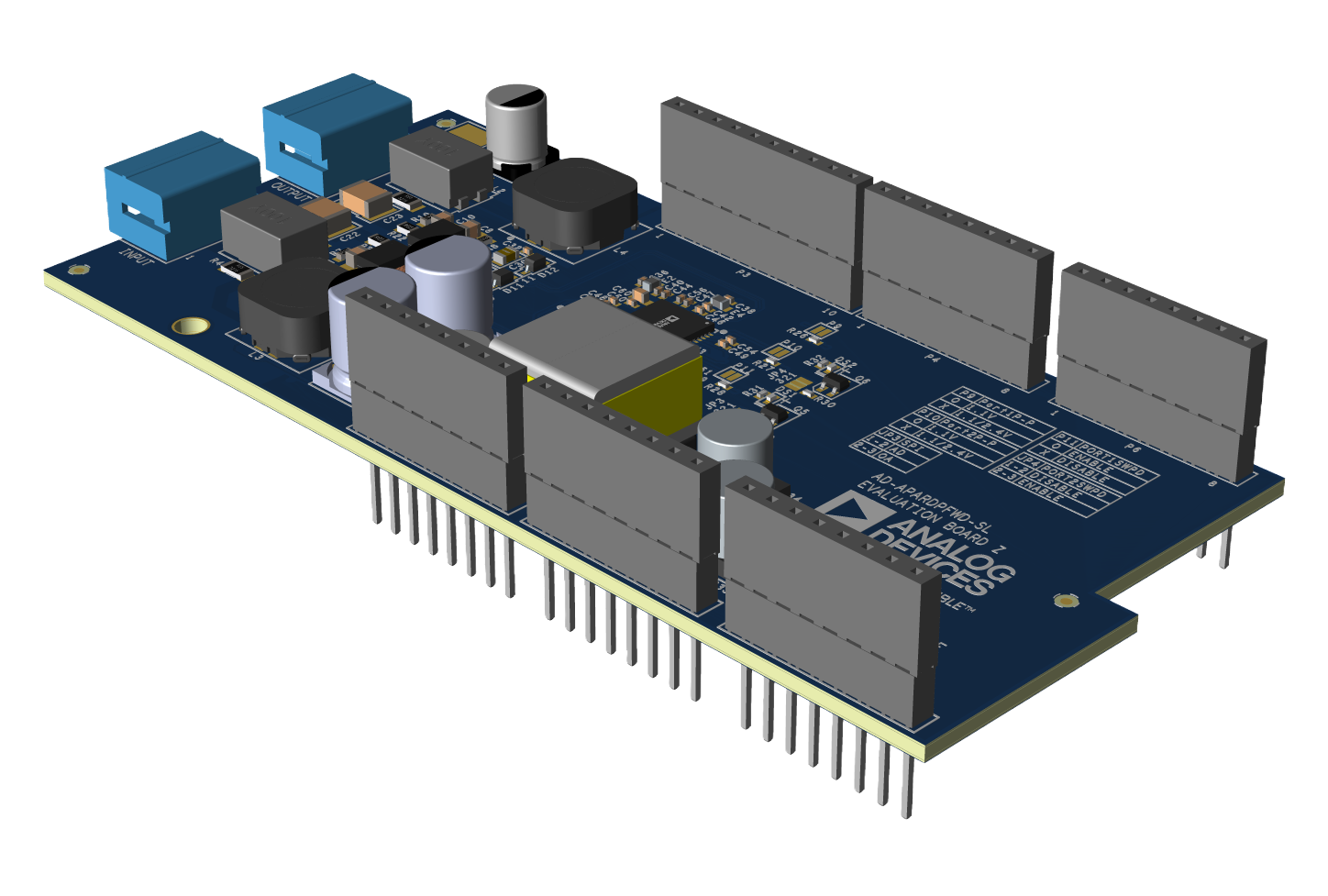

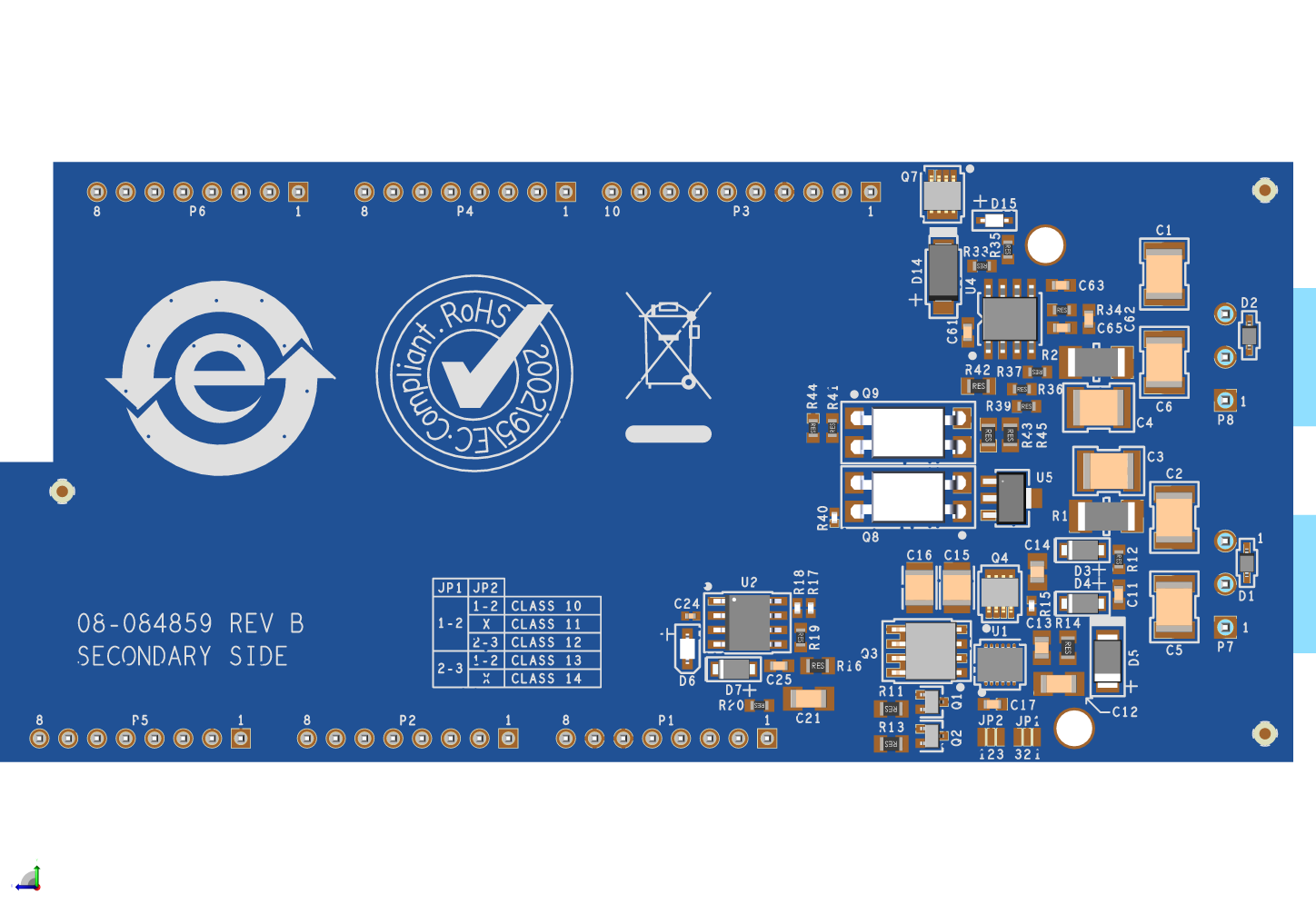

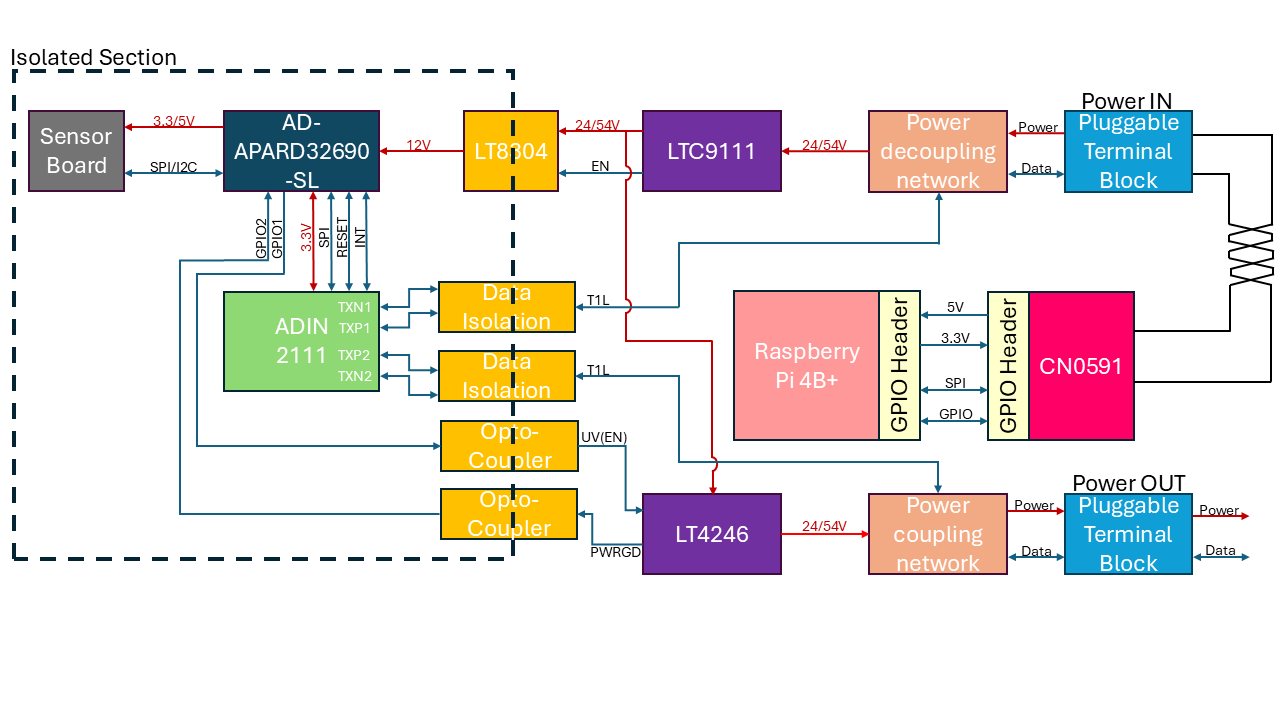

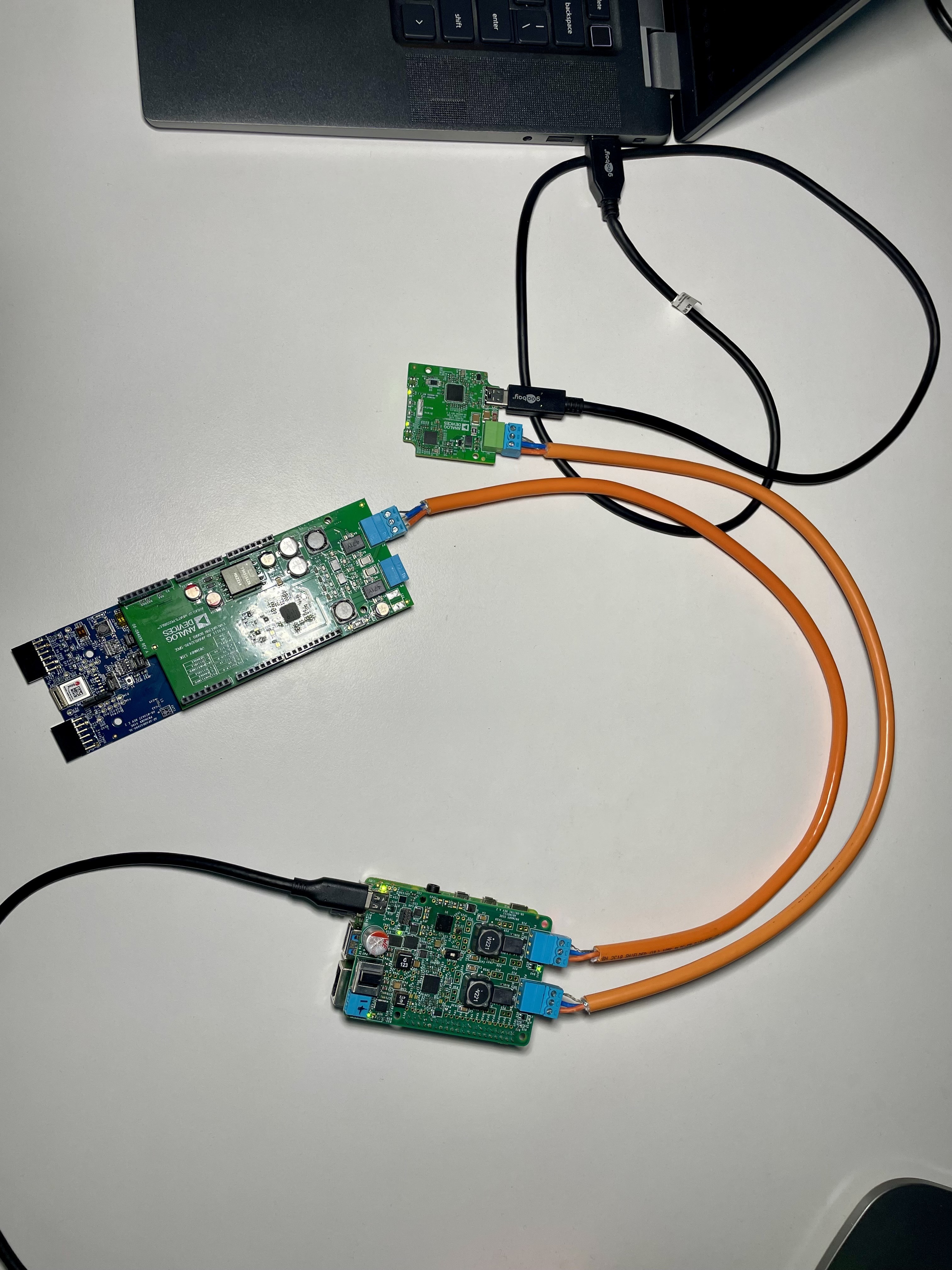

The AD-APARDPFW-SL uses 2 10BASE-T1L ports. One port is the input port (P7), which supplies power to the AD-APARD32690-SL platform board, and the other port is the output port (P8), which can be used to connect to another 10BASE-T1L device or to daisy chain multiple devices. The input port is connected to the LTC9111 SPoE PD controller, which extracts the SPoE power from the 10BASE-T1L cable and provides it to the LT8304 isolated flyback regulator. The LT8304 provides a regulated 12V.

Power is supplied to the AD-APARD32690-SL platform board via PIN8 of the P1 header.

The onboard ADIN2111 PHY provides the 10BASE-T1L connection to the host platform board. The ADIN2111 is connected to the AD-APARD32690-SL platform board via the P5 and uses the SPI4 port of the AD-APARD32690-SL.

The ADIN2111 supports selectable peak-to-peak transmit levels of 1.1V or 2.4V for each PHY. To select the desired level, configure the P9 and P10 solder jumpers for PHY1 and PHY2, respectively:

Disconnected: Sets the transmit level to 2.4V

Shorted: Sets the transmit level to 1.1V

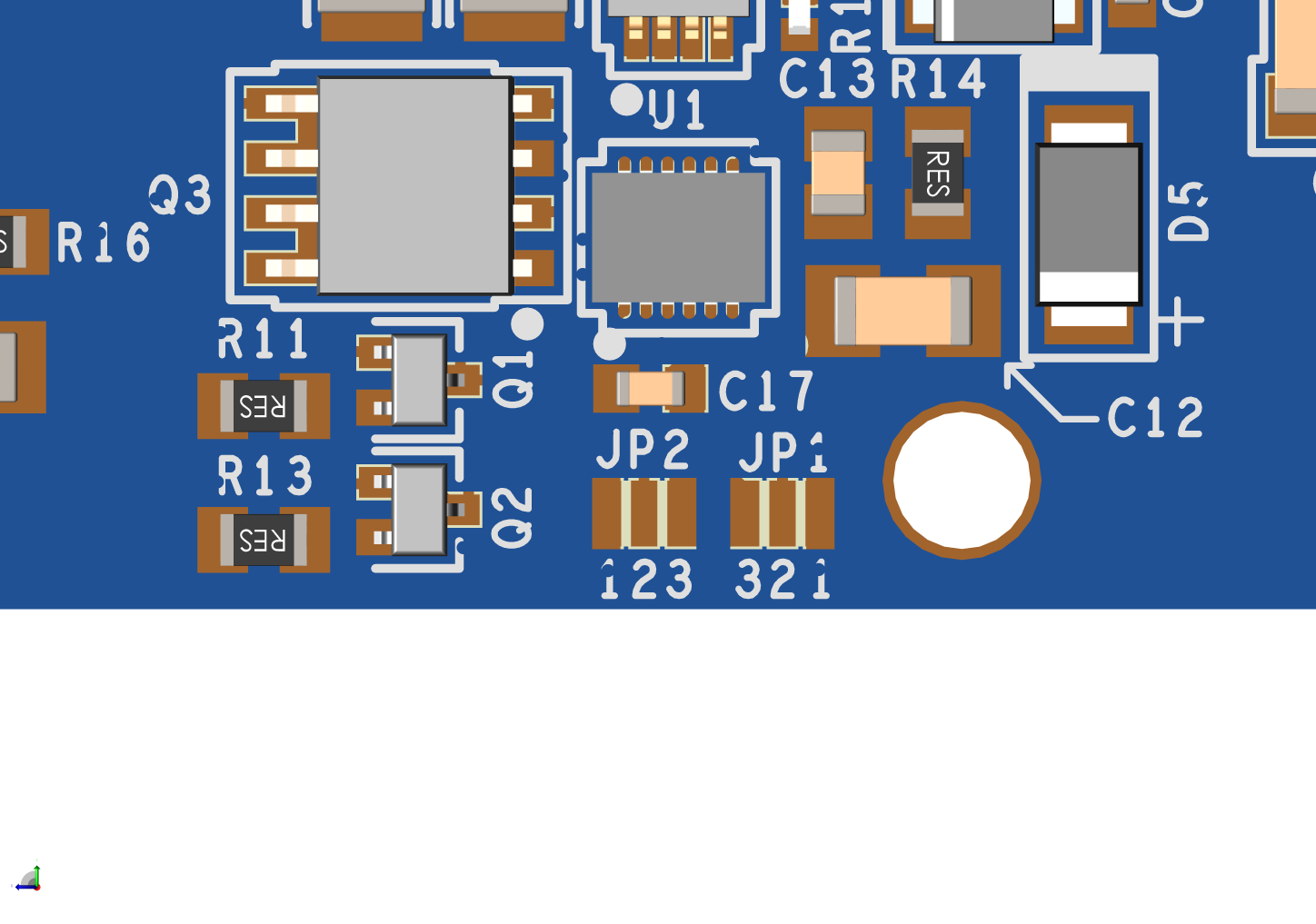

The generic SPI protocol is half duplex. Therefore, it is not possible to write frame data into the MAC_TX register and read from the MAC_RX register at the same time. To achieve full duplex transmission on Ethernet at 10 Mbps, OPEN Alliance SPI must be used. To select which SPI protocol to use, the JP3 solder jumper should be configured as follows:

JP3 Position |

SPI Mode |

Across 1 and 2 |

AD (Generic SPI) |

Across 2 and 3 |

OA (OPEN Alliance SPI) |

The ADIN2111 supports software power-down after power-up or reset for each port independently. To utilize this feature:

Short jumper P11 to enable the software power-down for PHY1.

In order to enable the software power-down for PHY2, configure JP4 solder jumper with the following settings

JP4 Position |

Software Power-down |

Across 1 and 2 |

Disabled |

Across 2 and 3 |

Enabled |