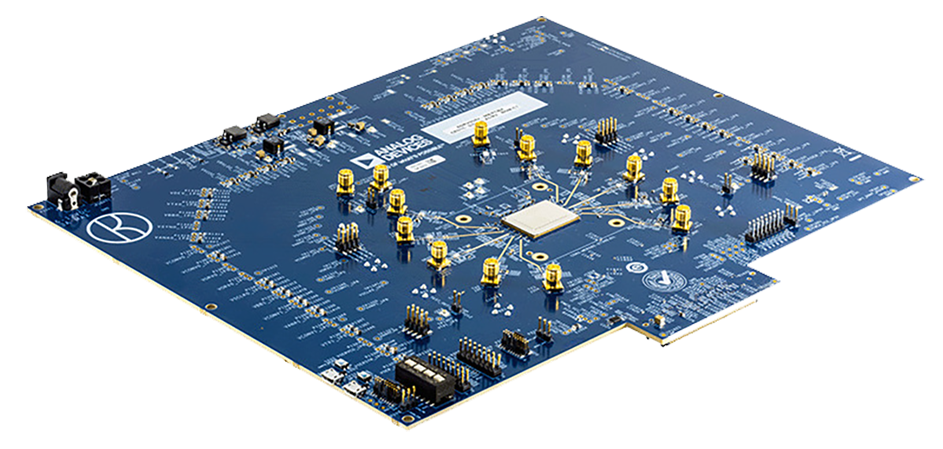

EVAL-ADRV904x

Integrated 8T8R RF Transceiver with Digital Pre-Distortion and Crest Factor Reduction.

Overview

The EVAL-ADRV904x, is an FMC radio card designed to showcase the ADRV9040 and ADRV9044, highly integrated, radio frequency (RF) agile transceivers offering 8 independently controlled transmitters, 2 observation receiver inputs for monitoring transmitter channels, 8 independently controlled receivers, integrated local oscillator (LO) and clock synthesizers, digital front-end (DFE) with crest factor reduction (CFR) and digital pre-distortion (DPD), and digital signal processing functions providing a complete transceiver solution.

The device provides the high radio performance and low-power consumption demanded by cellular infrastructure applications and massive MIMO base stations, offering advanced DFE capabilities on an integrated ARM Cortex-A55 quad-core processor.

Features:

Both chips feature:

8 differential transmitters & 8 differential receivers

2 differential observation receivers

Support for TDD and FDD applications

LO tunable range: 450 MHz to 7100 MHz

RF frequency bands:

Low Band (LB): 600 MHz to 2800 MHz

Mid Band (MB): 1.8 GHz to 4.8 GHz

High Band (HB): 4.5 GHz to 6 GHz

Integrated Digital Front-End (DFE) with CFR and digital pre-distortion

ARM Cortex-A55 quad-core processor for DFE algorithms (DPD, CLGC, VSWR)

JESD204B and JESD204C digital interface with fixed and floating-point data format support

Zero-IF (ZIF) architecture

Complete ADRV9040/ADRV9044 radio cards for evaluation

FMC connector for FPGA integration

Fully integrated fractional-N RF synthesizer

Fully integrated clock synthesizer

Applications:

3G/4G/5G TDD and FDD massive MIMO

Macro and small cell base stations

Software defined radios

Wireless infrastructure

Recommendations

People who follow the flow that is outlined, have a much better experience with things. However, like many things, documentation is never as complete as it should be. If you have any questions, feel free to ask on our EngineerZone forums, but before that, please make sure you read our documentation thoroughly.

To better understand the ADRV9040 / ADRV9044, we recommend to use the EVAL-ADRV904x evaluation board.

Table of contents

Using the evaluation board/full stack reference design that we offer:

Prerequisites - what you need to get started

-

Using the ZCU102/Zynq UltraScale+ MP SoC

Configure an SD Card with Kuiper

Linux Applications

Design with the ADRV9040/ADRV9044

Hardware in the Loop / How to design your own custom BaseBand

Resources for designing a custom ADRV9040/ADRV9044-based platform software

For Linux software:

About the device driver:

ADRV904x Linux device driver (not yet mainlined; source at drivers/iio/adc/koror/adrv904x.c) and how to customize it

About the device tree:

About the JESD204 utilities:

Changing the VCXO frequency and updating the default RF Transceiver Profile

HDL reference design which you must use in your FPGA.

Additional documentation about SDR Signal Chains - The math behind the RF

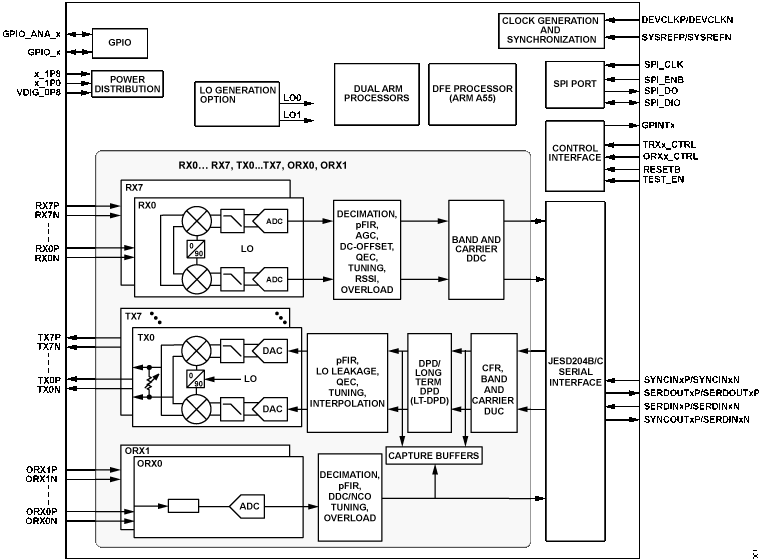

Block diagram

The ADRV9040/ADRV9044 features a zero-IF (ZIF) architecture that provides wide bandwidth with dynamic range suitable for contiguous and non-contiguous multicarrier applications. The transceiver includes:

8 transmitter channels with integrated DACs and DPD/CFR

8 receiver channels with integrated ADCs

2 observation receiver channels for transmitter monitoring

Integrated RF and clock synthesizers

Integrated ARM Cortex-A55 quad-core processor for DFE

JESD204B/C digital interface

SPI control interface

General purpose I/O and interrupts

Videos

Software Defined Radio using the Linux IIO Framework

ADI articles

Four Quick Steps to Production: Using Model-Based Design for Software-Defined Radio:

Part 2 - Mode S Detection and Decoding Using MATLAB and Simulink

Part 3 - Mode S Signals Decoding Algorithm Validation Using Hardware in the Loop

Part 4 - Rapid Prototyping Using the Zynq SDR Kit and Simulink Code Generation Workflow

About JESD standard:

MathWorks webinars

Warning

All the products described on this page include ESD (electrostatic discharge) sensitive devices. Electrostatic charges as high as 4000V readily accumulate on the human body or test equipment and can discharge without detection. Although the boards feature ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality. This includes removing static charge on external equipment, cables, or antennas before connecting to the device.